플립플롭(Flip-flop)은 디지털 전자공학에 속하는 용어로, 1비트의 정보를 저장하는 데 사용되는 전자부품이다.

플립플롭의 도식적 표현

- 플립플롭은 순차 회로이기 때문에 입력은 두 개의 매개변수를 기반으로 합니다. 하나는 현재 입력이고 다른 하나는 이전 상태의 출력입니다.

- 두 개의 출력이 있으며 둘 다 서로 보완됩니다.

- 0 또는 1의 두 가지 안정적인 상태 중 하나일 수 있습니다.

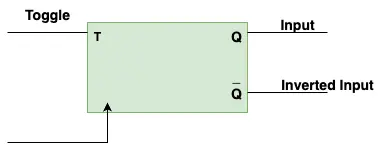

플립플롭의 기본 다이어그램

T플립플롭이란 무엇인가요?

- T 플립플롭, 더 정확하게 말하면 토글 플립플롭(Toggle Flip Flop)으로 알려져 있습니다. 입력에 따라 출력을 토글할 수 있기 때문입니다.

- 티 여기에 약자 비녀장 .

- 토글은 기본적으로 비트가 1에서 0으로 또는 0에서 1로 반전됨을 나타냅니다.

- 여기서는 이 플롭을 작동시키기 위해 클록 펄스가 공급되므로 클록 플립플롭이 됩니다.

T 플립플롭의 구성

우리는 세 가지 방법으로 T 플립을 구성할 수 있습니다.

- SR 플립플롭을 사용합니다.

- D 플립플롭을 사용합니다.

- JK 플립플롭을 사용하여

T 플립플롭을 구성하는 방법

아래와 같이 2개의 AND 게이트와 2개의 NOR 게이트가 필요한 SR 플립플롭을 사용한 T 플립플롭의 구성을 살펴보겠습니다.

T 플립플롭의 기본 블록 다이어그램

여기서 블록 다이어그램에는 토글 및 클럭 입력이 포함되어 있으며 Q 및 Q'는 보완된 입력입니다.

T 플립플롭의 작동

사례 1 : 의 말을하자, 티 = 0 그리고 클럭 펄스는 높은 즉, 1이면 AND 게이트 1과 AND 게이트 2 둘 다의 출력은 다음과 같습니다. 0 , 게이트 3 출력은 큐 그리고 마찬가지로 게이트 4 출력은 큐' 따라서 Q와 Q'의 값은 모두 이전 값과 동일합니다. 홀드 상태 .

사례 2 : 의 말을하자, 티=1 , AND 게이트 1의 출력은 다음과 같습니다. (T * 시계 * Q) , T와 클록이 모두 1이므로 AND 게이트 1의 출력은 다음과 같습니다. 큐 , 마찬가지로 AND 게이트 2의 출력은 다음과 같습니다. (T * 시계 * Q') 즉., 큐' . 이제 게이트 3 출력은 (Q'+Q)' Q'가 0이라고 가정하면 게이트 3 출력은 (0+Q)' 즉 큐' 마찬가지로 게이트 4 출력은 (Q+Q')' Q'는 0이므로 게이트 4 출력은 Q'가 됩니다. 0 Q'는 0이기 때문입니다. 따라서 이 경우 출력이 토글된다고 말할 수 있습니다. 티=1 .

T 플립플롭의 진리표

- 여기서 T는 토글 입력, Q는 현재 상태 입력, Qt+1은 다음 상태 출력입니다.

- 여기에서 Toggle(T)이 0일 때마다 다음 상태 출력(Qt+1)이 현재 상태 입력(Q)과 동일하다는 것을 알 수 있습니다.

- 토글(T)이 1일 때마다 다음 상태 출력(Qt+1)은 현재 상태 입력(Q)의 보완이 되며 이는 토글됨을 의미합니다.

특성 방정식

- 특성 방정식은 현재 상태를 기준으로 플립플롭의 다음 상태가 무엇인지 알려줍니다.

- 특성방정식을 얻기 위해 K-Map을 구성하면 다음과 같다.

- 위의 K-Map을 풀면 특성 방정식은 다음과 같습니다. Q(n+1) = TQn' + T'Qn = T XOR Qn

여기 테이블

여기 테이블(Excitation Table)은 기본적으로 플립플롭이 현재 상태에서 다음 상태로 가기 위해 필요한 여기(Excitation)에 대해 알려줍니다.

- 여기서 T가 0일 때마다 Qt+1은 입력 Q와 동일합니다.

- 그리고 T가 1일 때마다 Qt+1은 입력 Q에 대한 보완입니다.

T 플립플롭의 응용

디지털 시스템에는 T 플립플롭의 수많은 응용 프로그램이 있으며 다음과 같습니다.

- 카운터 : 카운터에 사용되는 T 플립플롭입니다. 카운터는 디지털 시스템에서 발생하는 이벤트 수를 계산합니다.

- 데이터 저장고 : T 전원이 꺼졌을 때 데이터를 저장하는 데 사용되는 메모리를 생성하는 데 사용되는 플립플롭입니다.

- 동기 논리 회로 : T 플립플롭은 클록 신호에 따라 이진 데이터에 대한 연산을 수행하는 회로인 동기 논리 회로를 구현하는 데 사용할 수 있습니다. T 플립플롭을 사용하여 논리 회로의 작동을 클록 신호에 동기화함으로써 회로의 동작을 예측 가능하고 신뢰할 수 있게 만들 수 있습니다.

- 주파수 분할 : 클럭 신호의 주파수를 2로 나누는 데 사용됩니다. 플립플롭은 클럭 신호가 하이에서 로우로 또는 로우에서 하이로 전환될 때마다 출력을 토글하므로 클럭 주파수를 2로 나눕니다.

- 시프트 레지스터 : T 플립플롭은 이진 데이터를 한 방향으로 이동하는 데 사용되는 시프트 레지스터에 사용될 수 있습니다.

결론

이 기사에서 우리는 플립플롭의 기본부터 시작하여 실제로 플립플롭이 무엇인지 설명한 다음 T 플립플롭에 대해 논의했습니다. T 플립플롭을 구성할 수 있는 세 가지 두 가지 방법은 기본 블록 다이어그램입니다. T 플립플롭의 작동 , 그것은 진리표, 특성 방정식 및 여기 테이블이며 마지막에는 T 플립 플롭의 응용에 대해 논의했습니다.